Hello,

I am a first year graduate student classically thrown into learning LabVIEW, so I would much appreciate some help with the code I am trying to work out. To give you an idea I started watching the tutorials on creating loops in February. For reference I am on LabVIEW 2014 and using a CRio-9066 with 8 modules and 256 total digital outputs.

The goal of the code is to 1) generate on/off times for the state of the outputs on the FPGA VI and 2) to communicate this with the FPGA VI in real time. The reason the code is on a computer VI and not contained on the FPGA is because I need to use a normal distrbution function (which has inputs mean and standard deviation and outputs a value accordingly) to determine the timing. This is easily achieved on the computer, but not so easily achieved on the FPGA interface. It is essential that each output follows it's own unique timing function for my purposes.

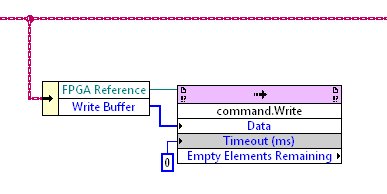

The way the code works is that each output has it's own while loop containing a two-frame timed loop (see attached.) A sub-VI I made (with a sun icon, see attached) outputs a timing value each time it is called, and this value delays the next iteration and during this delay sets the value of the local variable as true or false (on or off.) The state of the local variable is continuously communicated with the FPGA VI using a read/write control elsewhere in the program. The FPGA VI itself is a very simple VI which has boolean switches attached to each desired output.

This code works very well for 128 outputs. However, when I try to use it for all 256 outputs it does not work. The VI does not report any errors, however about half of the loops are apparently not executing. My suspicion was that there is a limit to the number of processors that can be simultaneously utilized to execute loops in a VI, so I split the VI into two parts, each with 128 outputs communicating with the same FPGA VI. Again, I had the same issue. I am not sure if this is due to processor overuse or UI latency in labview (since the front panel is rather cumbersome.) Any suggestions would be greatly appreciated.

One thought I had to work around this is to create a VI which generates timing values and stores them in an array. Then I could create a simple VI on the FPGA which reads these values and assigns a true or false state to the output accordingly. However, when I pasted the array into the FPGA VI I was returned the following error: "The FPGA module does not support variable-sized array on the front panel of the top-level VI." Any suggestions for working around this would be greatly appreciated as well.

Any thoughts, comments or insight would be greatly appreciated. I am new to this so I realize my code is probably inefficient and such, so any tips would be awesome. Thank you.